Nvidia "doubled" the int32 / FP cores for Ampere and Ada, but that's a bit of a stretch, not all of them can be used. There's so many things that can change in an SM that core count is a meaningless metric. Lastly we show that our optimized MCM-GPU is 26.8% faster than an equally equipped Multi-GPU system with the same total number of SMs and DRAM bandwidth. Most importantly, the optimized MCM-GPU design is 45.5% faster than the largest implementable monolithic GPU, and performs within 10% of a hypothetical (and unbuildable) monolithic GPU. Our evaluation shows that the optimized MCM-GPU achieves 22.8% speedup and 5x inter-GPM bandwidth reduction when compared to the basic MCM-GPU architecture.

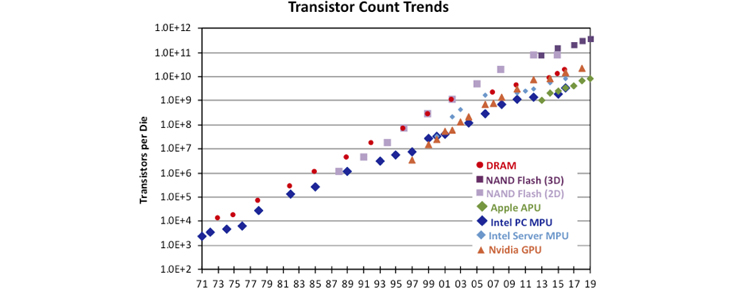

We then propose three architectural optimizations that significantly improve GPM data locality and minimize the sensitivity on inter-GPM bandwidth. We lay out the details and evaluate the feasibility of a basic Multi-Chip-Module GPU (MCM-GPU) design. Specifically, we propose partitioning GPUs into easily manufacturable basic GPU Modules (GPMs), and integrating them on package using high bandwidth and power efficient signaling technologies. To address this need, in this paper we demonstrate that package-level integration of multiple GPU modules to build larger logical GPUs can enable continuous performance scaling beyond Moore's law. However, the need for higher performing GPUs continues to exist in many domains. As Moore's law slows down, and the number of transistors per die no longer grows at historical rates, the performance curve of single monolithic GPUs will ultimately plateau. Historically, improvements in GPU-based high performance computing have been tightly coupled to transistor scaling.

#CPU TRANSISTOR COUNT 2025 SERIES#

The specific number and configuration of these dies are yet to be determined, but this approach will grant NVIDIA greater flexibility in customizing chips for consumers, mirroring AMD’s intentions with the Instinct MI300 series

This suggests that NVIDIA will employ advanced packaging techniques, dividing GPU components into separate dies. Kopite has not disclosed further details at this point, but it is said that GB100 GPU might feature twice as many cores as GB102, both are data-center GPUS.Īdditionally, there has been mention of GB100, the data-center GPU for Blackwell, adopting a Multi Chip Module (MCM) design.

While it remains unclear whether this pertains to both data-center and gaming series, the core count for Blackwell is anticipated to remain relatively unchanged, while the underlying GPU clusters will undergo significant structural modifications. NVIDIA is gearing up to introduce several GPU processors, with no major alterations to core counts, but there are hints of a significant restructuring of the GPU architecture.Īccording to the latest series of tweets from Kopite, Blackwell is not expected to feature a substantial increase in core counts. In contrast to the Hopper/Ada architecture, Blackwell is set to extend its reach across both datacenter and consumer GPUs. NVIDIA’s upcoming GPU architecture, codenamed Blackwell, is poised to be the successor to Ada Lovelace.

0 kommentar(er)

0 kommentar(er)